User Tools

This is an old revision of the document!

System Plots

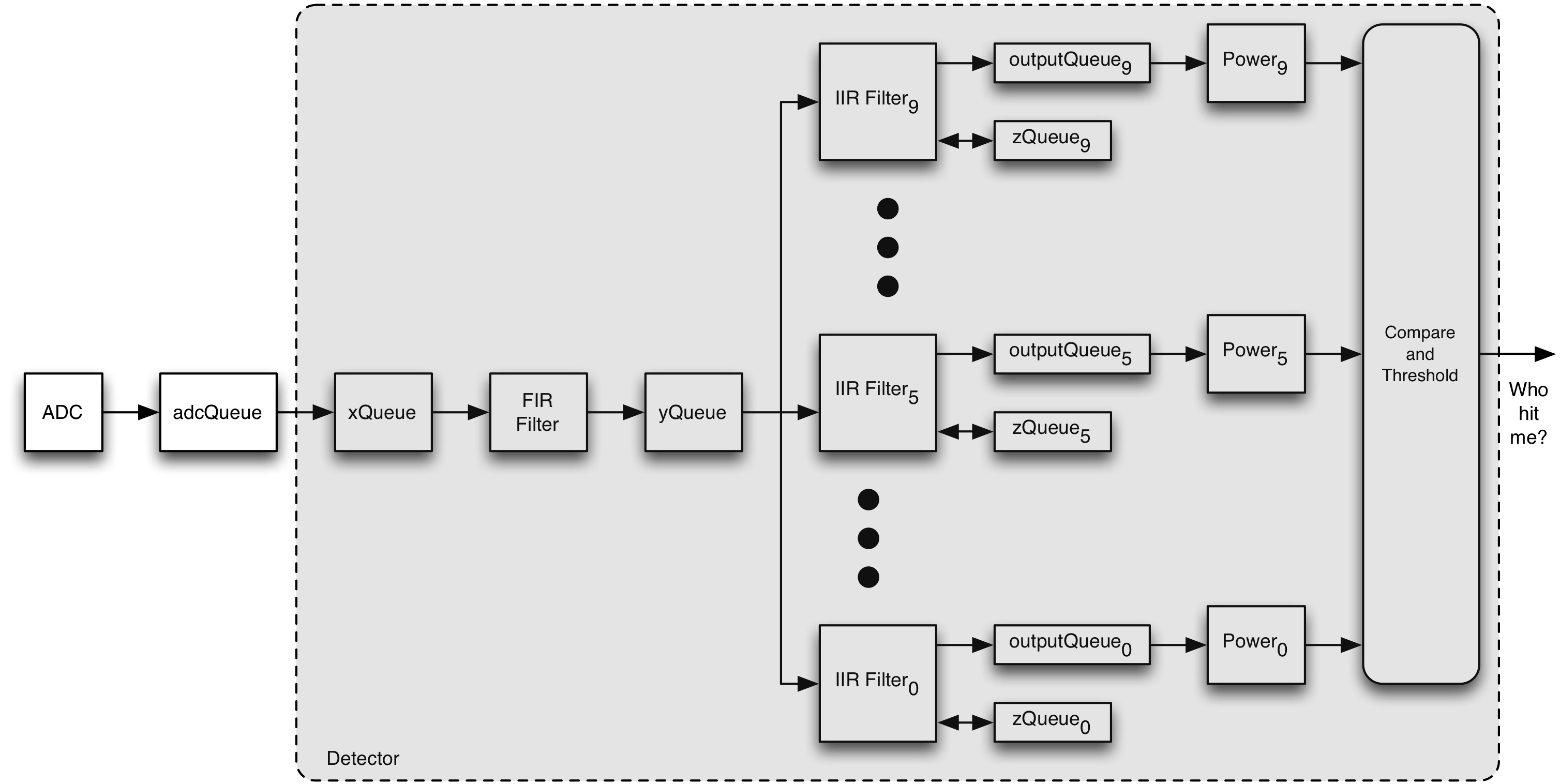

This is basic block diagram of the system.

The basic process is the following:

- Read numbers from the receiver board using the ADC at a rate of FS=100 kHz

- Low pass filter the samples (using an FIR filter)

- Down sample the data to a rate of FS=10 kHz

- Filter the data through the 10 bandpass filters (using 10 IIR filters)

- Compute a running power

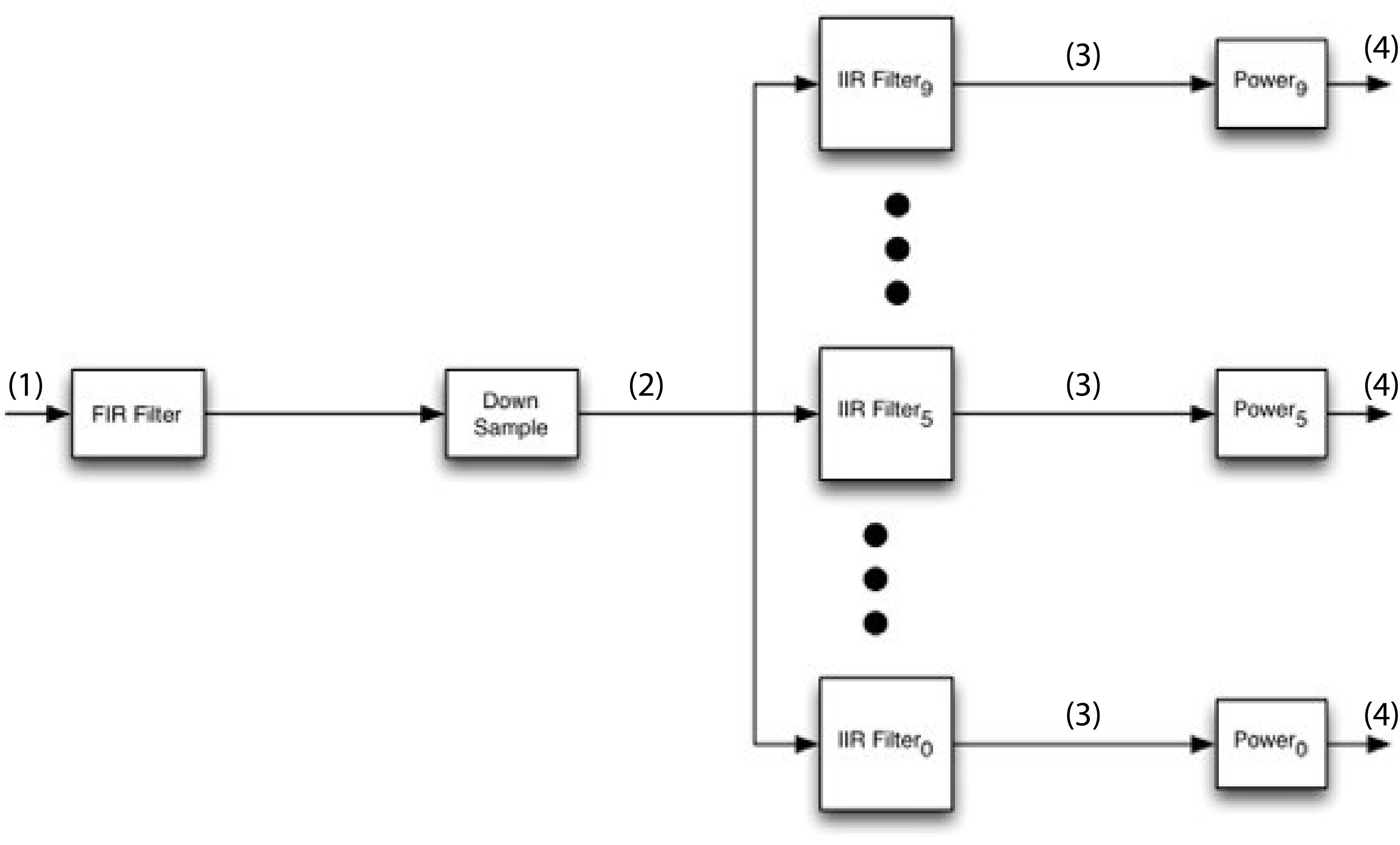

To better understand this process let's look at what the data would look like at various points in the design. The following block diagram is a simplified version of the previous block diagram. In this block diagram the queues have been removed since those are related to the way that the data structures are implemented.

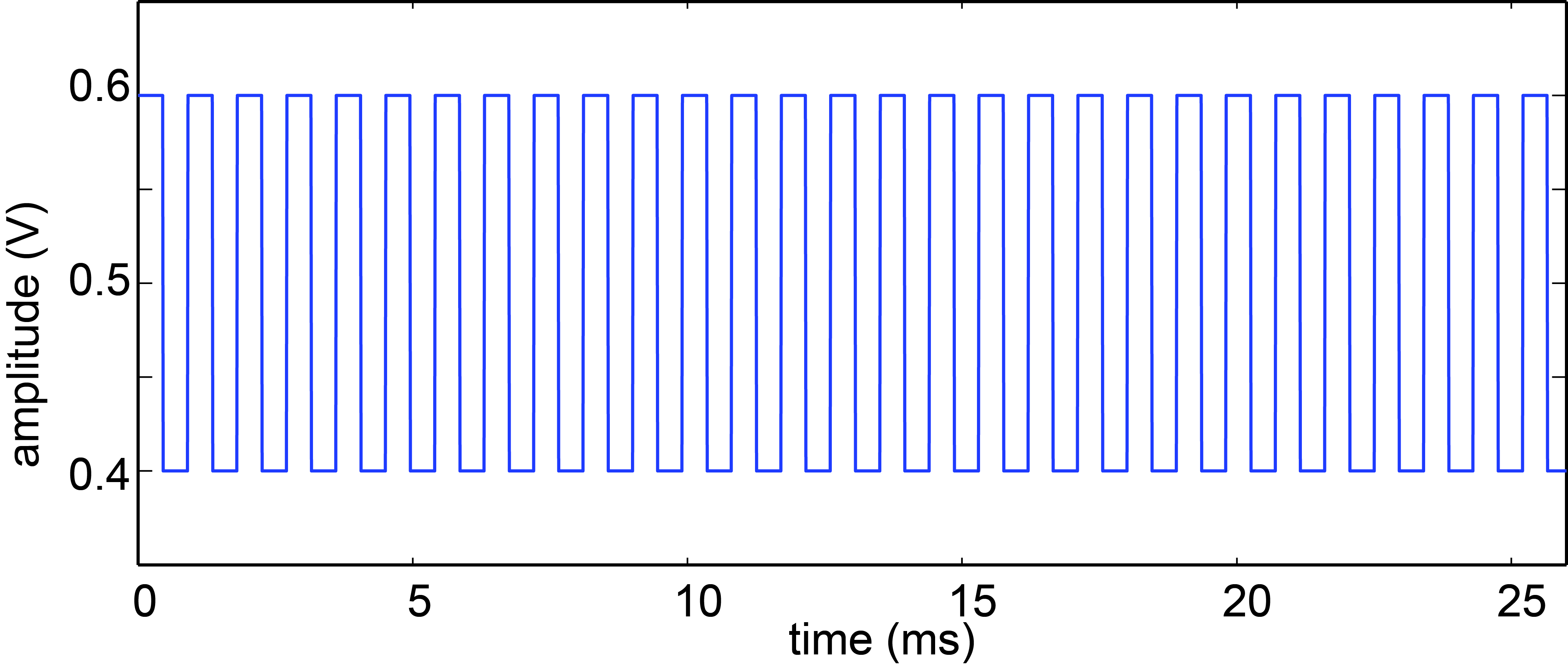

We are going to start by looking at a signal that is a square wave without any noise. This initial plot is at location (1) on the block diagram. This signal is a square wave with frequency of f=1111 Hz, amplitude of 0.2 V peak-to-peak, offset voltage of 0.5 V, and a sampling frequency of FS=100 kHz. We have zoomed in on the first 25 ms of time so that it is easy to see the square wave oscillations

The first block is the FIR low pass filter. The purpose of the low pass filtering is discussed in a separate low pass filtering page. After the low pass filtering the signal is down sampled to FS=10 kHz. In the actual system the FIR filtering and the down-sampling are accomplished at the same time.

This plot shows both the low pass filtering and the down sampled signal. This is labeled as point (2) in the block diagram. The filtering starts at 0 since the data is initialized at zero. It quickly follows the original signal.